# The Design of Control Enabled UART

Mahesh d gowdhar<sup>1</sup>, ch shekar<sup>2</sup>, narendara chary<sup>3</sup>

1.2.3 ECE Department, SreeDattha Institute of Engineering & Science

Abstract:- UART is a simple bus communication system that is used as worldwide transmission for the slow receiver and fast sender. The design of UART can be of the different methods we are using the advance design FSM method for the design of the UART .we introduces the new logic for the devices that which works for the different clocks. Whenever a clock source is driving by the circuit elements like gates and flops that cannot able to drive the cascaded circuit elements generally we need sub systems like clock gating or buffer plane. In order to avoid the turbulences that occurred for the transmitting the data for the different user defined frequencies depend on the receiver we are introducing new concept called control enables. The proposed UART is designed using the VHDL and simulated with model-sim and synthesized by Xilinx

#### I. INTRODUCTION

Simple asynchronous serial bus that used for the receiving and transmit data between the processor and controllers generally we prefer the UART as the protocol. By this we can easily transmit the parallel data transmission serially with user or design specified rates. UART can be well known, cost effective and simple it efficient for the point to point communications. For the transmission and reception in UART they are different design methods, in present VLSI systems complexity is increases the design issues and more over the features are also gains the transmitting based on the receiver speed by using the baud-rate generators as a part of design. To the processor, the UART appears as an 8-bit read-write parallel port that performs serial-to-parallel conversions for the processor, and vice versa for the peripheral. The UART allows reliable data transfer at high speeds with its 16-byte first in, first out (FIFO) input register. The FIFO feature can buffer up to 16 bytes at a time, which improves serial communications by preventing data overruns in applications. The implementation of UART the serial communication is done with high data rate and no interrupts. The UART 16550 serial communication interface device receives data and converts data from serial to parallel, where as the transmitter performs parallel to serial conversion.

This paper organizes as follows, session I gives the introduction to the paper session II describes about UART description with the FSM's and parity enable and disables third session deals with the proposed control enables and session IV deals with the results and discussion followed by conclusion

#### II. UART DATA TRANSMISSION

For the serial asynchronous data communication between the remote embedded systems UART can be used efficiently. This makes a channel to communicate processor/controller to asynchronous transmission A UART communication module as transmitter it converts the parallel form of data into the serial format by making the frames by word length by adding the star bit, stop bit, sometimes parity based on requirement

generally the world length can be 5, 6, 7 or 8 bits the Parity can be odd or even There are different flavors UART in the industry. Some of them may contain FIFOs in the receiver/transmitter modules and some of have different bit modes like 9 Data bits mode (Start bit + 9 Data bits + Parity + Stop bits). Generally the basic UART design consists of a receiver and transmitter modules. Parallel-to- serial conversion by receiving the 8-bit data from CPU (processor/controller) is performed by the transmitter. Serial-to-parallel conversion is done by the receiver module asynchronously received data frame which sent as the serial data format

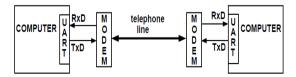

Figure 1. Basic Application of UART

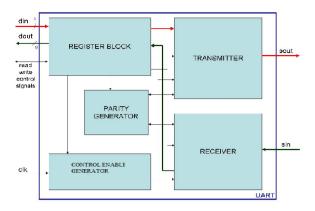

Figure 2: Block Diagram of UART

UART module internally consists of register block, parity generator, transmitter and receiver.

Register block is used to store the data temporarily for serial transmission and parallel sending to  $D_{\text{out}}$

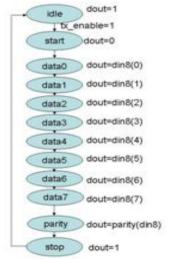

The transmitter module internally consists of the FSM module which function to transmit the data serially with parity if necessity by parity enable

It internally consists of 12 states

| STATE         | OPERATION                   | I                 |                |          |       |      |         |          |         |

|---------------|-----------------------------|-------------------|----------------|----------|-------|------|---------|----------|---------|

| IDEL          |                             |                   | no             | operatio | on st | tate | (system | synchron | ization |

|               | and wait for re             | equest will be do | one)           |          |       |      |         |          |         |

| START         | sends the start             | bit               |                |          |       |      |         |          |         |

| DATA0         | sends the 0 <sup>th</sup> p | osition bit as ou | itput to sout  |          |       |      |         |          |         |

| DATA1         | sends the 1 <sup>th</sup> p | osition bit as ou | itput to sout  |          |       |      |         |          |         |

| DATA2         | sends the 2 <sup>th</sup> p | osition bit as ou | itput to sout  |          |       |      |         |          |         |

| DATA3         | sends the 3 <sup>th</sup>   | position bit as o | output to sout |          |       |      |         |          |         |

| DATA4         | sends the 4 <sup>th</sup>   | position bit as o | output to sout |          |       |      |         |          |         |

| DATA5         |                             | position bit as o |                |          |       |      |         |          |         |

| DATA6         | sends the 6 <sup>th</sup>   | position bit as o | output to sout |          |       |      |         |          |         |

| DATA7         | sends the 7 <sup>th</sup>   | position bit as o | output to sout |          |       |      |         |          |         |

| <b>PARITY</b> |                             | provides          | the            | parity   | bit   | (odd | parity  | of       | the     |

|               | input                       | 8-bit)            | based          | on       | reque | st   | of      | user     | by      |

|               | enabling the                | parity enable     |                |          |       |      |         |          |         |

| STOP          | sends the sto               | p bit             |                |          |       |      |         |          |         |

Figure3:Transmitter FSM

The receiver also internally consists of the FSM this receives the data serially and sent as parallel to Dout. The receiver operation also similar to transmitter FSM but in receiver FSM receives the each bit in per stateIn receiver parity calculation and comparison can be carried out if the parity enable is high only then it performs

the parity otherwise it shifts the particular state and sends the frame to processor/controller.

Figure3:Reciver FSM

## III. PROPOSED CONTROL ENABLES

In control enable module internally consist of the default counter circuit in it. It generally counts the numbers from '0' to the 'n' N- can be depend on the rate of transmission. The counter table and control enable generation table is shown below

| count | CE1 | CE2 | CE3 |

|-------|-----|-----|-----|

| 000   | 0   | 0   | 0   |

| 001   | 0   | 0   | 1   |

| 010   | 0   | 1   | 0   |

| 011   | 0   | 1   | 1   |

| 100   | 1   | 0   | 0   |

| 101   | 1   | 0   | 1   |

| 110   | 1   | 1   | 0   |

| 111   | 1   | 1   | 1   |

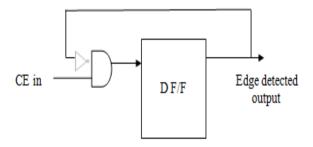

This control enables are positive edge detected by the edge detection circuit. Only single operation can be performed even though CE value is high for more than one clock cycle.

The edge detection can be performed by the following circuit shown in fig

Figure4: edge detection circuit

Figure 5 UART transmitter waveforms

Figure 5 shows the waveforms of the UART transmitter. The present state indicates the current state of the state machine. It traverses from IDLE to STOP state. The data input can be seen on din and corresponding serial output is given on sout. Since parity\_en = 1, parity bit is appended to data.

Figure 6 UART receiver waveforms

Fig. 6 shows the receiver waveforms. The state transitions are similar to transmitter. The serial data input comes on sin and output data is dout. The data is sampled when data\_rx\_done = '1'.

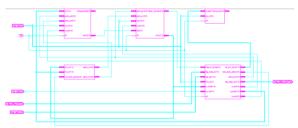

Figure 7 Blocks inside the Developed Top Level UART Design

The internal blocks available inside the design includes parity generator, control enable, register block, transmitter and Receiver which were clearly shown in the above schematic level diagram. Inside each block the gate level circuit will be generated with respect to the modelled HDL code.

## V. CONCLUSION

UART can be designed by the FSM'S and the operation can be performed with synchronized control enables which can makes transmission easy with the different frequencies and baud rates efficiently without clock gating and internal buffers. This will be appropriate for the ASIC and FPGAs, more efficient for the FPGAs.

### **REFERENCES**

- [1]. Ritesh Kumar Agrawal and Vivek Ranjan Mishra "The Design of High Speed UART" 2013 IEEE Conference on Information and Communication Technologies

- [2]. Charles H. Roth, Jr, Digital System Design by using VHDL, PWS Publishing Company, 1998

- [3]. Samir Palintkar, Verilog HDL A Guide to Digital Design and Synthesis, Second Edition, Pearson Publication, 2011

- [4]. Tomasi, Wayne, Advanced electronic communication systems, Third Edition, Prentice-Hall, United States of America, 1994

- [5]. Michael D. Ciletti, Advanced Digital Design with the Verilog HDL, Second Edition, Prentice Hall, Second edition